# **Nios II Custom Instruction**

# **User Guide**

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com

Copyright © 2004 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap-

plication or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

UG-N2CSTNST-1.2

# Contents

| About this User Guide                                    | v    |

|----------------------------------------------------------|------|

| How to Find Information                                  |      |

| How to Contact Altera                                    |      |

| Typographic Conventions                                  |      |

| Chapter 1. Nios II Custom Instruction Overview           |      |

| Introduction                                             | 1–1  |

| Custom Instruction Overview                              |      |

| Implementing Custom Instruction Hardware                 |      |

| Implementing Custom Instruction Software                 | 1–4  |

| Custom Instruction Architectural Types                   |      |

| Combinatorial Custom Instruction Architecture            |      |

| Combinatorial Port Operation                             | 1–5  |

| Multi-Cycle Custom Instruction Architecture              |      |

| Multi-Cycle Port Operation                               |      |

| Extended Custom Instruction Architecture                 |      |

| Extended Custom Instruction Port Operation               | 1–10 |

| Internal Register File Custom Instruction Architecture   |      |

| Internal Register File Custom Instruction Port Operation | 1–12 |

| External Interface Custom Instruction                    | 1–12 |

| Chapter 2. Software Interface                            |      |

| Introduction                                             | 91   |

| Introduction                                   | 2 - 1 |

|------------------------------------------------|-------|

| Chapter Overview                               | 2-1   |

| Bit-Swap Custom Instruction — Example A        | 2-1   |

| Bit-Swap Custom Instruction — Example B        |       |

| Built in Functions & User-Defined Macros       |       |

| Custom Instruction Assembly Software Interface | 2-4   |

### Chapter 3. Implementing a Nios II Processor Custom Instruction

| 1 |

|---|

| 1 |

| 1 |

| 2 |

| 2 |

| 2 |

| 4 |

| 6 |

| 6 |

| 7 |

|   |

| VHDL & Verilog HDL Templates       A-1         VHDL Template       A-1         Verilog HDL Template       A-2         Custom Instruction Built-In Functions 1       B-1         Built-In Functions       B-1         Built-In Functions Returning Void       B-1         Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1       Hardware & Software Porting Considerations | Generate the SOPC Builder System & Compile in Quartus II Software       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| VHDL Template       A-1         Verilog HDL Template       A-2         Custom Instruction Built-In Functions 1       Built-In Functions 1         Built-In Functions Returning Void       B-1         Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1       C-1                                                  | Custom Instruction Templates 1                                          |

| VHDL Template       A-1         Verilog HDL Template       A-2         Custom Instruction Built-In Functions 1       Built-In Functions 1         Built-In Functions Returning Void       B-1         Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1       C-1                                                  | VHDL & Verilog HDL Templates                                            |

| Verilog HDL Template       A-2         Custom Instruction Built-In Functions 1       Built-In Functions 1         Built-In Functions       B-1         Built-In Functions Returning Void       B-1         Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1       C-1                                             | VHDL Template A-1                                                       |

| Built-In Functions       B-1         Built-In Functions Returning Void       B-1         Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1       Hardware & Software Porting Considerations                                                                                                                            |                                                                         |

| Built-In Functions Returning Void       B-1         Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1         Hardware & Software Porting Considerations       C-1                                                                                                                                                                                                          | Custom Instruction Built-In Functions 1                                 |

| Built-In Functions Returning Void       B-1         Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1         Hardware & Software Porting Considerations       C-1                                                                                                                                                                                                          | Built-In Functions                                                      |

| Built-in Functions Returning int       B-1         Built-in Functions Returning float       B-1         Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1         Hardware & Software Porting Considerations       C-1                                                                                                                                                                                                                                                              | Built-In Functions Returning Void B-1                                   |

| Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1       C-1                                                                                                                                                                                                                                                                                                                                                                                                                         | Built-in Functions Returning int                                        |

| Built-in Functions Returning a Pointer       B-2         Porting First- Generation Nios Custom Instructions to Nios II Systems 1       C-1                                                                                                                                                                                                                                                                                                                                                                                                                         | Built-in Functions Returning float B-1                                  |

| Hardware & Software Porting Considerations C-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                         |

| Hardware & Software Porting Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Porting First- Generation Nios Custom Instructions to Nios II Systems 1 |

| Hardware Porting Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Hardware & Software Porting Considerations C-1                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Hardware Porting Considerations                                         |

| Software Porting Considerations C-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Software Porting Considerations C-1                                     |

| C-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                         |

# About this User Guide

This user guide provides comprehensive information about  $Altera^{\circledast}$  Nios II custom instructions.

Table 1–1 shows the user guide revision history. December

| Table 1–1. Tutorial Revision History |                                                                           |  |

|--------------------------------------|---------------------------------------------------------------------------|--|

| Date                                 | Description                                                               |  |

| December 2004                        | Updates for the Nios II version 1.1 release.                              |  |

| September 2004                       | Updates for the Nios II version 1.01 release.                             |  |

| May 2004                             | First release of custom instruction user guide for the Nios II processor. |  |

### How to Find Information

- The Adobe Acrobat Find feature allows you to search the contents of a PDF file. Click the binoculars toolbar icon to open the Find dialog box

- Bookmarks serve as an additional table of contents

- Thumbnail icons, which provide miniature previews of each page, provide a link to the pages

- Numerous links, shown in green text, allow you to jump to related information

### How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                |

|--------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | (408) 544-7000 <i>(1)</i><br>(7:00 a.m. to 5:00 p.m. Pacific Time) |

| Product literature             | www.altera.com                                                 | www.altera.com                                                     |

| Altera literature services     | lit_req@altera.com (1)                                         | lit_req@altera.com (1)                                             |

| Non-technical customer service | (800) 767-3753                                                 | (408) 544-7000<br>(7:30 a.m. to 5:30 p.m. Pacific Time)            |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                     |

#### Note to table:

(1) You can also contact your local Altera sales office or sales representative.

## Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |  |  |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file.                                             |  |  |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75:<br>High-Speed Board Design.                                                                                                                                                                                                      |  |  |

| Italic type                                 | Internal timing parameters and variables are shown in italic type.<br>Examples: $t_{PIA}$ , $n + 1$ .                                                                                                                                                                                                                   |  |  |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type.<br>Example: <i><file name="">, <project name="">.<b>pof</b> file.</project></file></i>                                                                                                                                                    |  |  |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |  |  |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |  |  |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |  |  |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |  |  |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |  |  |

| ••                                          | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |  |  |

| $\checkmark$                                | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |  |  |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |  |  |

| CAUTION                                     | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                         |  |  |

|                                             | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |  |  |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |  |  |

| ••••                                        | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |  |  |

# 1. Nios II Custom Instruction Overview

### Introduction

With the Altera® Nios® II embedded processor, system designers can accelerate time-critical software algorithms by adding custom instructions to the Nios instruction set. With custom instructions, system designers can reduce a complex sequence of standard instructions to a single instruction implemented in hardware. System designers can use this feature for a variety of applications, e.g., to optimize software inner loops for digital signal processing (DSP), packet header processing, and computation-intensive applications. The Nios II CPU configuration wizard, which is accessed via the Quartus® II software's SOPC Builder, provides a graphical user interface (GUI) used to add up to 256 custom instructions to the Nios II processor.

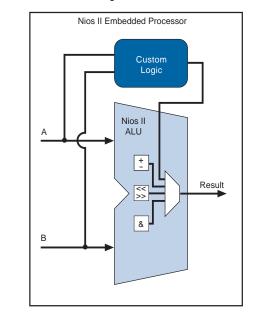

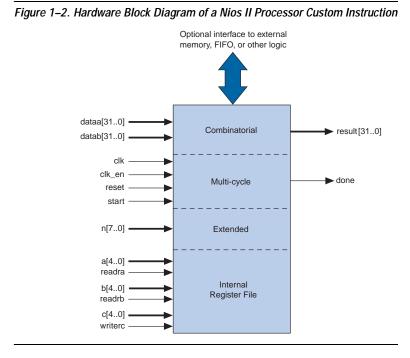

The custom instruction logic connects directly to the Nios II arithmetic logic unit (ALU) as shown in Figure 1–1.

Figure 1–1. Custom Instruction Logic Connects to the Nios II ALU

This chapter:

|                                   | <ul> <li>Describes the Nios II processor custom instruction feature</li> <li>Discusses the requirements for implementing a custom instruction in hardware &amp; software</li> <li>Defines custom instruction architectural types</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | For information regarding custom instructions software interface, refer to<br>Chapter 2, Software Interface. A tutorial with design files and step-by-<br>step instructions for implementing a custom instruction, is found in<br>Chapter 3, Implementing a Nios II Processor Custom Instruction.                                                                                                                                                                                                                                                                                                                                                             |

| Custom<br>Instruction<br>Overview | With Nios II processor custom instructions, system designers are able to take full advantage of the flexibility of FPGAs to meet system performance requirements. Custom instructions allow system designers to add custom functionality to the Nios II processor ALU.                                                                                                                                                                                                                                                                                                                                                                                        |

|                                   | Nios II processor custom instructions are custom logic blocks adjacent to<br>the ALU in the CPU's data path. This gives system designers the ability<br>to tailor the Nios II processor core to meet the needs of a particular<br>application. System designers have the ability to accelerate time critical<br>software algorithms by converting them to custom hardware logic blocks.<br>Because it is easy to alter the design of the FPGA-based Nios II processor,<br>custom instructions provide an easy way to experiment with<br>hardware/software trade-offs during an embedded system's<br>implementation phase—rather than the specification phase. |

### Implementing Custom Instruction Hardware

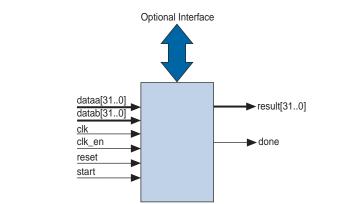

Figure 1–2 is a hardware block diagram of a Nios II processor custom instruction.

The basic operation of Nios II custom instruction logic is to receive input on the dataa[31..0] and/or datab[31..0] and drive out the result on its result[31..0] port. The designer generates the custom instruction logic that produces the results.

The Nios II processor supports different architectural types of custom instructions. Figure 1–2 lists the additional signals that accommodate different architectural types. Only the ports used for the specific custom instruction implementation are required.

Figure 1–2 also shows an optional interface to external logic. The interface to external logic allows designers to include a custom interface to system resources outside of the Nios II processor data path.

### Implementing Custom Instruction Software

The Nios II processor custom instruction software interface is simple and abstracts the details of the custom instruction from the programmer. For each custom instruction, the Nios II integrated development environment (IDE) produces a macro that is defined in the system header file. You can call the macro from C or C++ application code as a normal function call and you do not need to program assembly to access custom instructions. Custom instructions can also be accessed via the Nios II processor assembly code.

For more information, refer to Chapter 2, Software Interface.

## Custom Instruction **Architectural** Types

Г

There are different custom instruction architectures available to suit the application's requirements. The architectures range from a simple, singlecycle combinatorial architecture to an extended variable-length, multicycle custom instruction architecture. The chosen architecture determines what the hardware interface looks like.

Table 1-1 shows custom instruction architectural types, application, and the associated hardware interface.

| Table 1–1. Custom Instruction Architectural Types, Application & Hardware Interface |                                                                                                |                                                                                                                                                      |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Architectural Type                                                                  | Application                                                                                    | Hardware Interface                                                                                                                                   |  |

| Combinatorial                                                                       | Single clock cycle custom logic<br>blocks                                                      | dataa[310], datab[310],<br>result[310]                                                                                                               |  |

| Multi-cycle                                                                         | Multi clock cycle custom logic block of fixed or variable durations                            | <pre>dataa[310], datab[310], result[310], clk, clk_en, start, reset, done</pre>                                                                      |  |

| Extended                                                                            | Custom logic blocks that are<br>capable of performing multiple<br>operations                   | <pre>dataa[310], datab[310],<br/>result[310], clk, clk_en,<br/>start, reset, done, n[70]</pre>                                                       |  |

| Internal Register File                                                              | Custom logic blocks that access<br>internal register file for input and/or<br>output           | <pre>dataa[310], datab[310],<br/>result[310], clk, clk_en,<br/>start, reset, done, n[70],<br/>a[40], readra, b[40], readrb,<br/>c[40], writerc</pre> |  |

| External Interface                                                                  | Custom logic blocks that interface to<br>logic outside of the NIOS II<br>processor's data path | Standard custom instruction signals, plus user-<br>defined interface to external logic.                                                              |  |

This section discusses the basic functionality and hardware interface of each custom instruction architecture type listed in Table 1-1.

### **Combinatorial Custom Instruction Architecture**

Combinatorial custom instruction architecture consists of a logic block that is able to complete in a single clock cycle.

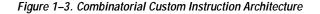

Figure 1–3 shows a block diagram of a combinatorial custom instruction architecture.

The Figure 1–3 combinatorial custom instruction diagram uses dataa[31..0] and datab[31..0] ports as inputs and drives the results on the result[31..0] port. Because the logic is able to complete in a single clock cycle, control signals are not needed.

Table 1–2 lists the combinatorial custom instruction signals.

| Table 1–2. Combinatorial Custom Instruction Signals |           |          |                                        |

|-----------------------------------------------------|-----------|----------|----------------------------------------|

| Signal Name                                         | Direction | Required | Purpose                                |

| dataa[310]                                          | Input     | No       | Input Operand to custom instruction    |

| datab[310]                                          | Input     | No       | Input Operand to custom<br>instruction |

| result[310]                                         | Output    | Yes      | Result from custom instruction         |

The only required port for combinatorial custom instructions is the result [31..0] port. The dataa [31..0] and datab [31..0] signals are optional, and should only be included if the application requires input operands. If only a single data port is needed, use dataa [31..0].

### Combinatorial Port Operation

This section describes the combinatorial custom instruction hardware interface port operation. Figure 1–4 shows the combinatorial custom instruction hardware interface timing diagram.

In Figure 1–4, the CPU presents the dataa [31..0] and datab [31..0] ports on the rising edge of the CPU clock. The CPU reads the result [31..0] port on the following rising edge of the CPU clock.

The Nios II processor issues combinatorial custom instructions speculatively, and therefore combinatorial custom instructions cannot have an external interface.

Combinatorial custom instructions can be further optimized by utilizing the extended custom instructions architecture. Refer to "Extended Custom Instruction Architecture" on page 1–9.

Figure 1–4. Combinatorial Custom Instruction Interface Timing Diagram

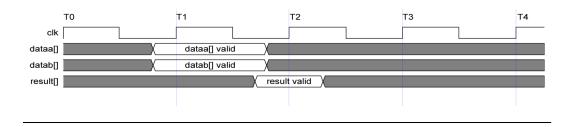

### Multi-Cycle Custom Instruction Architecture

Multi-cycle, or sequential, custom instructions consists of a logic block that requires two or more clocks to complete an operation. Multi-cycle custom instruction can complete in either a fixed- or variable-number of clock cycles. Additional control signals are required for multi-cycle custom instructions. See Table 1–3.

Figure 1–5 shows the multi-cycle custom instruction block diagram.

As stated previously, multi-cycle custom instructions can be either fixed or variable length in duration:

- Fixed length: You specify the required number of clock cycles during system generation

- Variable length: The start and done signals are used in a handshaking scheme to determine when the custom instruction execution is complete.

Table 1–3 lists multi-cycle custom instruction signals.

| Table 1–3. Multi-Cycle Custom Instruction Signals |           |          |                                                                      |

|---------------------------------------------------|-----------|----------|----------------------------------------------------------------------|

| Signal Name                                       | Direction | Required | Application                                                          |

| clk                                               | Input     | Yes      | System clock                                                         |

| clk_en                                            | Input     | Yes      | Clock enable                                                         |

| reset                                             | Input     | Yes      | Synchronous reset                                                    |

| start                                             | Input     | No       | Signals custom instruction logic to start execution                  |

| done                                              | Output    | No       | Custom instruction logic signals the CPU that execution is complete. |

| dataa[310]                                        | Input     | No       | Input operand to custom instruction                                  |

| datab[310]                                        | Input     | No       | Input operand to custom instruction                                  |

| result[310]                                       | Output    | No       | Result from custom instruction                                       |

As indicated in Table 1–3, the clk, clk\_en, and reset signals are required for multi-cycle custom instructions. However, the start, done, dataa[31..0], datab[31..0], and result[31..0] signals are optional, and should only be used if required for the specific application.

### Multi-Cycle Port Operation

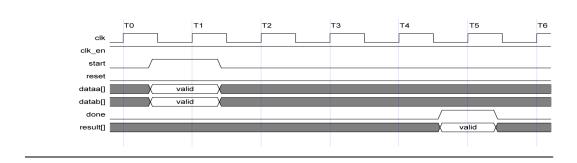

The section provides operational details for the multi-cycle, custom instruction hardware interface. Figure 1–6 shows the multi-cycle custom instruction timing diagram.

- The CPU asserts the active high start port on the first clock cycle of execution when the custom instruction issues through the ALU. At this time, the dataa[31..0] and datab[31..0] signals have valid values and remain valid throughout the duration of the custom instruction execution.

- Fixed or variable length custom instruction port operation:

- Fixed length: The CPU asserts start, waits a specified number of clock cycles, and then reads result [31..0]. For an *n*-cycle operation, the custom logic block must present valid data on the (*n*-1) rising edge after the start signal is asserted.

- Variable length: The CPU waits until the active high done signal is asserted. The CPU reads the result [31..0] port on the clock edge that done is asserted. The custom logic block should present data on the result [31..0] port on the same clock that the done signal is asserted.

- The Nios II system clock feeds the custom logic block's clk signal, and the Nios II master reset feeds the active high reset signal. The reset signal is asserted only when the whole Nios II system is reset.

- The custom logic block should use the active high clk\_en signal as a conventional clock qualifier signal and should ignore all clock rising edges while clk\_en is deasserted.

- Any port in the custom logic block that is not recognized as a custom instruction signal is considered to be an external interface signal.

- Multi-cycle custom instructions can be further optimized utilizing the extended, internal register file, and external interface custom instructions. Refer to "Extended Custom Instruction Architecture" on page 1–9, "Internal Register File Custom Instruction Architecture" on page 1–10, or "External Interface Custom Instruction" on page 1–12.

Figure 1–6. Multi-Cycle Custom Instruction Timing Diagram

### **Extended Custom Instruction Architecture**

Extended custom instruction architecture allows for a single custom logic block to output results for different operations. Extended custom instructions make use of the N field to specify which logic operation is performed by the custom logic. The 8-bit wide N field in the op-code allows for 256 different operations for a single block of custom logic.

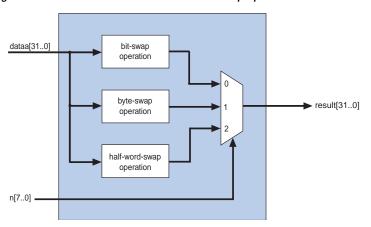

Figure 1–7 is a block diagram of an extended custom instruction with bitswap, byte-swap, and half-word-swap operations.

Figure 1–7. Extended Custom Instruction with Swap Operations

The Figure 1–7 swap operations are performed on data coming in via the dataa[31..0] port. The n[7..0] port is used as a select signal on an output multiplexer to select which operation is presented to the result [31..0] port.

Extended custom instructions can be either combinatorial or multi-cycle custom instructions. To implement an extended custom instruction, simply add an n [7..0] port to the interface for your custom instruction logic. The bit width of the n [7..0] port is a function of a number of operations the extended custom instruction can perform.

#### Extended Custom Instruction Port Operation

The n [7..0] port behaves similarly to the dataa [31..0] port. The CPU presents the n [7..0] port for execution on the rising edge of clock when start is asserted, and the n [7..0] port remains stable throughout the execution of the custom instruction. Each custom instruction's bit-width of the n [7..0] port is a function of the number of unique operations the custom logic block is able to perform.

All other custom instruction port operations remain the same.

### Internal Register File Custom Instruction Architecture

The Nios II processor allows custom instruction logic to access its own internal register file for I/O, which provides you the flexibility to specify if operands should be read from the Nios II processor's register file or the custom instructions internal register file. In addition, results from operations can be written to the local register file rather than the Nios II processor's register file.

Internal registers accessing custom instructions use readra, readrb, and writerc to determine if I/O should take place between the Nios II register file or an internal register file. Additionally, signals a [4..0], b [4..0], and c [4..0] specify which internal registers to read from and/or write to. For example, if readra is deasserted (i.e., read from the internal register), a [4..0] provides an index to the internal register file.

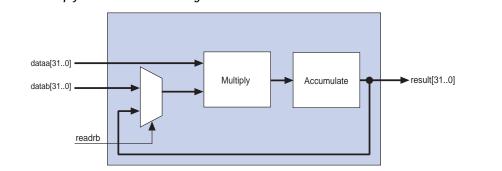

Figure 1–8 shows a simple, multiply-accumulate custom logic block.

When readrb is deasserted, the multiplication of dataa [31..0] and datab [31..0] occurs, and the results are stored in the accumulate register. Those results can be read back by the Nios II processor, or alternatively that value in the accumulator can be read as input to the multiplier by asserting readrb.

Table 1–4 lists the internal register file custom instructions signals. The signals are optional and should only be used if required by the application.

| Table 1–4. Internal Register File Custom Instruction Signals |           |          |                                                                                                                                                                                               |

|--------------------------------------------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                                  | Direction | Required | Application                                                                                                                                                                                   |

| readra                                                       | Input     | No       | If readra is high, dataa [310] and<br>datab [310] are supplied by the Nios II CPU. If<br>readra is low, custom instruction logic should read<br>the internal register file indexed by a [40]. |

| readrb                                                       | Input     | No       | If readrb is high, dataa [310] and<br>datab [310] are supplied by the Nios II CPU. If<br>readrb is low, custom instruction logic should read<br>the internal register file indexed by a [40]. |

| writerc                                                      | Input     | No       | Signal's custom instructions to write result of c [40] to custom instruction internal register file.                                                                                          |

| a[40]                                                        | Input     | No       | Custom instruction internal register file index                                                                                                                                               |

| b[40]                                                        | Input     | No       | Custom instruction internal register file index                                                                                                                                               |

| c[40]                                                        | Input     | No       | Custom instruction internal register file index                                                                                                                                               |

#### Internal Register File Custom Instruction Port Operation

The readra, readrb, writerc, and a [4..0], b [4..0], and c [4..0]ports behave similarly to dataa [31..0]. When the start signal is asserted, the CPU presents the readra, readrb, writerc, a [4..0], b[4..0], and c[4..0] signals on the rising edge of the CPU clock. All the ports remain stable throughout the execution of the custom instructions.

To determine how to handle register file I/O, custom instruction logic should read the active high readra, readrb, and writerc signals. The a[4..0], b[4..0], and c[4..0] ports should be used as register file indexes. When readra or readrb are not asserted, the custom instruction logic should ignore the corresponding a [4..0] or b[4..0] port. When writec is not asserted, the CPU ignores the value driven on the result [31..0] port.

All other custom instructions port operations remain the same.

### External Interface Custom Instruction

Figure 1-9 shows that the Nios II processor custom instructions allow you to add an interface to communicate with logic outside of the processor's data path. At system generation, any signals that are not recognized as custom instruction signals will propagate out to the top level of the SOPC Builder module where external logic can access the signals.

Figure 1–9. Custom Instructions Allow the Addition of an External Interface

December 2004

Figure 1–9 shows a multi-cycle custom instruction that has an external memory interface. Because the custom instruction logic is able to access memory external to the CPU, it extends the capabilities of the custom instruction logic.

Custom instruction logic can perform various tasks, e.g., store intermediate results, or read memory to control the custom instruction operation. The optional external interface also provides a dedicated path for data to flow into, or out of, the CPU. For example, custom instruction logic can feed data directly from the CPU's register file to an external FIFO memory buffer, bypassing the processor's data bus.

# 2. Software Interface

| Introduction        | The Nios II processor custom instruction details are abstracted from the application code. During the build process the Nios II integrated development environment (IDE) automatically generates macros that allow easy access from application code to custom instructions. |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Chapter<br>Overview | <ul> <li>This chapter provides custom instruction software interface details including:</li> <li>Bit-swap custom instruction examples</li> <li>Built-in functions &amp; user-defined macros</li> <li>Custom instruction assembly software interface</li> </ul>               |  |  |  |  |

|                     | Bit-Swap Custom Instruction — Example A<br>Example A shows a portion of the <b>system.h</b> header file that defines the<br>macro for a bit-swap custom instruction. This bit-swap example uses one<br>32-bit input and performs only one function:                          |  |  |  |  |

|                     | #define ALT_CI_BSWAP_N 0x00                                                                                                                                                                                                                                                  |  |  |  |  |

|                     | <pre>#define ALT_CI_BSWAP(A)builtin_custom_ini(ALT_CI_BSWAP_N,(A))</pre>                                                                                                                                                                                                     |  |  |  |  |

|                     | In bit-swap Example A, <code>ALT_CI_BSWAP_N</code> is defined to be <code>0x0</code> , which is the custom instruction's op-code number. The <code>ALT_CI_BSWAP(A)</code> macro is mapped to a <code>gcc</code> built-in macro that takes a single argument.                 |  |  |  |  |

|                     | Bit-Swap Custom Instruction — Example B                                                                                                                                                                                                                                      |  |  |  |  |

|                     | The following bit-swap example illustrates a bit swap custom instruction used in application code.                                                                                                                                                                           |  |  |  |  |

|                     | <pre>1. #include "system.h" 2. 3. 4. int main (void) 5. { 6. int a = 0x12345678; 7. int a_swap = 0; 8. 9. a_swap = ALT_CI_BSWAP(a); 10. return 0; 11.}</pre>                                                                                                                 |  |  |  |  |

In this example, the **system.h** file is included on line 1 to locate the custom instruction macro definitions. Two integers are declared; one on line 6 and one on line 7. Integer a is passed as input to the bit swap custom instruction with the results loaded into a\_swap on line 9.

The bit-swap Example B accommodates most applications using custom instructions. The macros defined by the Nios II IDE only make use of c integer types. Occasionally, applications need to make use of input types other than integers, and therefore, need to pass expected return values other than integers.

The Nios II processor custom instructions allow you to define custom macros that allow for other 32-bit input types to interface with custom instructions.

### **Built in Functions & User-Defined Macros**

The Nios II processor uses gcc built-in functions to map to custom instructions. Using built-in functions allows for types other than integers to be used with custom instructions. There are 52 uniquely-defined, built-in functions to accommodate the different combinations of the supported types.

Refer to Appendix B, Custom Instruction Built-In Functions for more information on custom instruction's built-in functions.

Built-in functions have the following format:

\_\_builtin\_custom\_<return type>nparameter types>

Table 2–1 shows 32-bit input types supported by custom instructions as parameters and return types, as well as the abbreviations used in the built-in function definition.

| Table 2–1. 32-Bit Input Types Support | by Custom Instructions         |

|---------------------------------------|--------------------------------|

| Input Type                            | Built-In Function Abbreviation |

| int                                   | i                              |

| float                                 | f                              |

| void *                                | p                              |

Example C shows the prototype definition for two built-in functions.

Example C:

void \_\_builtin\_custom\_nf (int n, float dataa); float \_\_builtin\_custom\_fnp(int n, void \*dataa);

In Example C, the \_builtin\_custom\_nf function takes an int and a float as inputs, and does not return a value. Whereas, the \_builtin\_custom\_fnp function takes an integer and a pointer as an input, and returns a float.

To support non-integer input types, you should define macros that map to the specific built-in function required for the application.

Refer to Appendix B, Custom Instruction Built-In Functions for a list of built-in functions.

Example D shows user-defined custom instruction macros used in an application.

Example D:

```

1. /* define void udef macro1(float data); */

2. #define UDEF MACRO1 N 0x00

3. #define UDEF MACRO1(A) builtin custom nf(UDEF MACRO1 N,

(A));

4. /* define float udef macro2(void *data); */

5. #define UDEF MACRO2 N 0x01

6. #define UDEF MACRO2(B) builtin custom fnp(UDEF MACRO2 N,

(B));

7.

8. int main (void)

9. {

10. float a = 1.789;

11. float b = 0.0;

12. float *pt a = &a;

13.

14. UDEF MACRO1(a);

15. b = UDEF MACRO2((void *)pt a);

16. return 0;

17. }

```

On lines 2 through 6, the user-defined macros are declared and mapped to the appropriate built-in functions. The macro UDEF\_MACRO1 takes a float as an input parameter and does not return anything. The macro UDEF\_MACRO2 takes a pointer as an input parameter and returns a float. Lines 14 and 15 show the use of the two user-defined macros.

### **Custom Instruction Assembly Software Interface**

The Nios II processor custom instructions are also accessible in assembly code. This section describes the assembly interface.

Custom instructions are R-type instructions with a 6-bit op-code, three 5-bit register index fields, and an 11-bit op-code-extension field. The 11-bit op-code extension field is broken into an 8-bit N field for the extended custom instruction and 3 bits for the readra, readrb and writerc bits.

Figure 2–1 is a diagram of the op-code for custom instructions, excerpted from the "Instruction Set Reference" chapter in the *Nios II Processor Reference Handbook.*

Figure 2–1. Op-Code for Custom Instructions Diagram

| 31 30 29 28 27      | 26 25 24 23 22                                         | 21 20 19 18 17                            | 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0         |

|---------------------|--------------------------------------------------------|-------------------------------------------|--------------------------------------------------|

| A                   | В                                                      | С                                         | I         I         N         uP OPCode = Custom |

| Instruction Fields: | readra = 1 if instruction<br>readrb = 1 if instruction | rea<br>wr<br>of operand A<br>of operand B | rwise<br>rwise                                   |

The assembler syntax for the custom instruction is:

custom N, xC, xA, xB

Where N is the custom instruction op-code number, xC is the destination register for the result [31..0] port, xA is operand1, and xB is operand2. To access the Nios II CPU's register file, replace x with r. To access a custom register file, replace x with c.

The following shows the syntax for two examples of custom instruction assembler calls:

Example 1: custom 0, r6, r7, r8 Example 2: custom 3, c1, r2, c4 Example 1 executes a custom instruction with an op-code number of 0. The contents of the Nios II processor register r7 and r8 are used as input with the results stored in the Nios II processor register r6.

Example 2 executes a custom instruction with an op-code number of 3. The contents of the Nios II processor register r2 and custom register c4 are used as inputs. The results are stored in the custom register c1.

# 3. Implementing a Nios II Processor Custom Instruction

| Introduction           | This chapter walks you through the process of implementing a Nios® II processor custom instruction, and illustrates the enormous time-savings that are possible with Nios II custom instructions.                                                                                             |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware &<br>Software | The instructions in this chapter require the following hardware and software:                                                                                                                                                                                                                 |

| Requirements           | <ul> <li>Quartus® II software version 4.1, SP1 or later</li> <li>Nios II development kit</li> <li>Nios development board, Stratix® II, Stratix, Stratix Professional, or Cyclone™ Edition</li> </ul>                                                                                          |

| Tutorial Files         | The tutorial design files are installed with the Nios II development kit.<br>The hardware design files are stored in the tutorials directory: <i><nios i="" ii="" kit<=""><br/><i>path&gt;</i>\<b>tutorials</b>\<b>Nios2_Custom_Instruction</b>\<i><board version=""></board></i>\</nios></i> |

|                        | Each development board has its own tutorial design file directory (see Table 3–1). The Quartus II project files are contained in the <b>quartus_project</b> directory and the hardware for the custom instruction is contained in the <b>rtl</b> directory.                                   |

|                        | Table 3–1. Design File Directories                                                                                                                                                                                                                                                            |

| Table 3–1. Design File Directo | ries                                         |

|--------------------------------|----------------------------------------------|

| Nios Development Board         | Tutorial Directory                           |

| Stratix II Edition             | niosII_stratixII_2s60_es                     |

| Stratix Edition                | niosII_stratix_1s10 & niosII_stratix_1s10_es |

| Stratix Professional Edition   | niosII_stratix_1s40                          |

| Cyclone Edition                | niosII_cyclone_1c20                          |

This tutorial uses the Nios II integrated development environment (IDE) software template design files located in the following directory:

<Nios II kit path>\examples\software\ci\_tutorial

The software files in this directory are copied to your working project directory in the Nios II IDE, so there is no need to move the files.

| Design Example:<br>Leading Zeros<br>Detector | The leading-zeros-detector design is a simple application that is relevant<br>to floating-point math algorithms. The number of leading zeros found in<br>floating point operands is used during the normalization process before<br>the floating point operation takes place.                                                                                                            |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                              | This design example counts the number of leading zeros of an array of numbers. Without Nios II custom instructions, the software algorithm loops until it finds the first 1, which takes several iterations and multiple CPU clocks cycles. However with Nios II custom instructions, the same algorithm can complete in a single clock cycle using priority encoder custom logic block. |  |  |  |  |

| Running the<br>Software                      | The following guides you through the steps required to run the leading-<br>zeros-detector-software algorithm, while providing an opportunity to see<br>the design's functionality and software algorithm's performance.                                                                                                                                                                  |  |  |  |  |

| Algorithm in<br>Nios II IDE                  | This section includes:                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                              | <ul><li>Creating a new Nios II IDE project</li><li>Building and downloading the software application</li></ul>                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                              | Creating a New Nios II IDE Project                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                              | In this section you will create a new Nios II IDE project using a software template. The example's design files are pre-installed with the Nios II development kit. To create a new Nios II IDE project, perform the following steps:                                                                                                                                                    |  |  |  |  |

|                                              | 1. Choose <b>Programs &gt;Altera &gt; Nios II Development Kit</b> < <i>version number</i> > <b>Nios II IDE</b> (Windows Start menu).                                                                                                                                                                                                                                                     |  |  |  |  |

|                                              | <ol> <li>Choose New &gt; C/C++ Application (File menu). The first page of<br/>the New Project wizard appears. See Figure 3–1 on page 3–3.</li> </ol>                                                                                                                                                                                                                                     |  |  |  |  |

|                                              | 3. From Select Project Template, select <b>Custom Instruction Tutorial</b> .                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                              | 4. Leave the default selection for the project's name and ensure that <b>Use Default Location</b> is checked.                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

#### Figure 3–1. New Project Window

| Name: ci_tutoria                                                                                                                                                                                                                                                     | ation    | utorials/Nios2 Custom Instruction/miosII strati                                                                                                                                                                                                                                                                                                                                                                      | 1 Browne                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Select Target Hardv<br>50PC Builder Syster<br>CPU:                                                                                                                                                                                                                   |          | ltera\kits\nios2\tutorials\Nios2_Custom_Instruct                                                                                                                                                                                                                                                                                                                                                                     | Browse                                                |

| Select Project Temp<br>Blank Project<br>Board Diagnostics<br>Custom Instruction<br>Count Binary<br>Dhrystone<br>Flash Tests<br>Hello Freestanding<br>Hello MicroC/OS-III<br>Hello MicroC/OS-III<br>Hello Wirdd<br>NTP Client<br>Telnet Server<br>MicroC/OS-III Messa | Tutorial | Description<br>Leading Zeros Custom Instruction Software<br>Details<br>This example exercises the leading zeros cus<br>instruction inded in the Custom Instruction<br>hardware design. The application counts the<br>of leading zeros on an array of values first u<br>simple software algorithm, and then using a<br>instruction to accelerate the algorithm. See<br>I Custom Instruction User Guide for additional | Tutorial<br>number<br>sing a<br>sustom<br>the Nios II |

- 5. Click **Browse** in Select Target Hardware. The **Select Target Hardware** dialog box appears.

- 6. Browse to the custom instruction tutorial hardware design for the Nios development board that you are targeting.

- 7. Choose the system.ptf SOPC Builder system file.

- 8. Click **Open** to return to the **New Project** wizard. The SOPC Builder System field from the Select Target Hardware window is now specified with the custom instruction project SOPC Builder system. (See Figure 3–1.) In addition, the CPU field now contains the name of the CPU in the system.

- 9. Click Finish.

At this point, the new Nios II project file creation is complete. Figure 3-2 shows that upon successful project creation, the C/C++ **Projects** window contains the following:

- Application project: **ci\_tutorial\_0**

- HAL software library for the custom instruction hardware: ci\_tutorial\_0\_syslib

- Nios II device drivers

For more information on the HAL software library, refer to the *Nios II Software Developer's Handbook*.

### **Building & Downloading the Software Application**

This section provides the steps to download the leading-zeros software application to the Nios development board.

Before the application is executed, you should examine the **leading\_zeros\_ci.c** file:

- The contents of main should include three sets of test data, i.e., best case, worse case, and random data sets that have the leading zeros counted and placed into another array.

- There are conditional compile statements based on the existence of the ALT\_CI\_LEADING\_ZERO\_DETECTOR symbol. This is the name of the macro that is defined when the leading-zeros custom instruction is added to the system later in the tutorial.

- 1. Choose **Run As** >**Nios II Hardware** (Run menu). The build process begins.

Depending on the current hardware image on the Nios development board, Nios II IDE might recognize that the current hardware image is not the image required for the tutorial design. If this occurs, the Nios II IDE displays an error message and launches the Quartus II Programmer (see Figure 3–3). If the Quartus II Programmer does not launch, skip to Step 8.

| 🟓 Start       | File                | Device | Checksum | Usercode | Program/<br>Verify | Blank- Examin | e Security |

|---------------|---------------------|--------|----------|----------|--------------------|---------------|------------|

| Stop          | 1custom_instruction |        | 004796C5 | FFFFFFF  | Configure          | Check         | Bit        |

| 🛺 Auto Detect |                     |        |          |          |                    |               |            |

| 🗙 Delete      |                     |        |          |          |                    |               |            |

| 쓷 Add File    |                     |        |          |          |                    |               |            |

| 👺 Change File |                     |        |          |          |                    |               |            |

| 🗣 Save File   |                     |        |          |          |                    |               |            |

| 😂 Add Device  |                     |        |          |          |                    |               |            |

| 🛍 Up          |                     |        |          |          |                    |               |            |

|               |                     |        |          |          |                    |               |            |

Figure 3–3. Quartus II Programmer Window

When the Nios II IDE detects that the SOPC Builder system for the current project differs from the SOPC Builder system on the board, you must download an appropriate configuration file for the FPGA.

To download a new FPGA configuration file—SRAM object file (**.sof**)—to the Nios development board, perform the following steps:

- 2. Choose Open (File menu). A Windows Explorer dialog box appears.

- 3. Select custom\_instruction.sof. See Figure 3–3.

- 4. Click **Open** to add the **custom\_instruction.sof** programming file to the Quartus II Programmer file list and return to the Quartus II Programmer.

- 5. From the file list, turn on **Program/Configure** for the **custom\_instruction.sof** programming file. See Figure 3–3.

- 6. Choose Start (Processing menu) to download the programming file.

Your Altera programming hardware must first be configured correctly before you can click the **Start** button. If necessary, click **Hardware Setup...** to configure your programming hardware.

- 7. Exit the Quartus II Programmer and return to the Nios II IDE.

- In the Nios II IDE, choose Run As > Nios II Hardware (Run menu). This will start the build process and download the software image to the development board.

After the image is downloaded, the terminal will display the results of running 500 samples through the leading zeros detector in software. The worse case number is if all the samples are a value of  $0 \times 1$ . The best-case numbers are for the case of  $0 \times 80000000$ . The random case is random samples. The following is an example of the three sets of test data:

Implementing Custom Instruction Hardware in SOPC Builder This section walks you through the process of implementing Nios II custom instructions in hardware, and also provides custom instruction tool-flow explanations.

To implement the Nios II custom instruction for the leading-zeros design, you must:

- 1. Open the custom instruction tutorial hardware design.

- 2. Add the leading-zeros custom instruction logic to the Nios II CPU.

- 3. Generate the SOPC Builder system and compile the design in Quartus II.

### **Open The Custom Instruction Hardware Design**

- 1. Choose **Programs** > **Altera** > **Quartus II** <*version*> (Windows Start menu).

- 2. Choose **Open Project...** (File menu).

- 3. Browse to the quartus\_project directory for your board.

- 4. Choose the **custom\_instruction.qpf** and click **Open**.

- 5. Choose SOPC Builder...(Tools menu) to start SOPC Builder.

### Add The Leading-Zeros Custom Instruction Logic

This section walks you through the process of adding a custom instruction to an SOPC Builder system, and also provides custom instruction tool-flow explanations.

1. Select **cpu\_0** in the **Altera SOPC Builder System Contents** page. See Figure 3–4.

Figure 3–4. SOPC Builder System Contents Page

| 📒 Altera SOPC Builder - system                                                     |              |                                              |                                                  |               |            |        |

|------------------------------------------------------------------------------------|--------------|----------------------------------------------|--------------------------------------------------|---------------|------------|--------|

| File System Module View Tools H                                                    | lelp         |                                              |                                                  |               |            |        |

| System Contents More "cpu_0" Setting:                                              | s Syst       | em Generation                                |                                                  |               |            |        |

| Altera SOPC Builder  Altera SOPC Builder  Autor face to User Logic  Avaion Modules | Target       | Nos Development Board, Cyclone (EP1C20) Targ | et Device Family. Cyclone System Clock Frequency | /: <b>5</b> 0 | MHz        |        |

|                                                                                    | Use          | Module Name                                  | Description                                      | Base          | End        | IRQ    |

|                                                                                    | V            |                                              | Nios II Processor - Altera Confidential          | 0x00010000    | 0x000107FF |        |

|                                                                                    | $\checkmark$ | ⊞ sys_clk_timer                              | Interval timer                                   | 0x00100800    | 0x0010081F |        |

|                                                                                    |              | ∃ high_res_timer                             | Interval timer                                   | 0x00010820    | 0x0001083F |        |

|                                                                                    |              | ⊞ jtag_uart                                  | JTAG UART                                        | 0x00010800    | 0×00010807 |        |