L2 S4 – CLM 2012-2013 D. Etiemble

# TD4 : Logique structurée et logique en tranches

#### 1. Utilisation de PLA

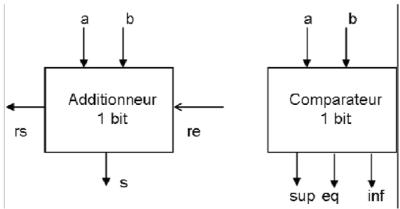

Donner les tables de vérité de l'additionneur 1 bit (entrées a, b et re, sorties s et rs) et du comparateur 1 bit de la Figure 1. Donner l'implantation de ces deux opérateurs sous forme de PLA

Figure 1: Additionneur et comparateur 1 bit.

### 2. Comparateurs

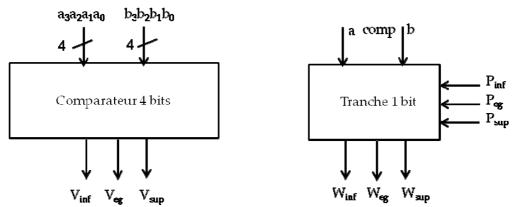

Ce type de circuit (Figure 2) compare des entiers naturels codés suivant le code usuel (base 2), sur n bits.

Figure 2 : Comparateur

- 1. Décomposer la fonction logique  $a_{n-1}...a_1a_0 < b_{n-1}...b_1b_0$  en partant des bits de poids fort.

- 2. En déduire l'organisation d'un comparateur 4 bits basé sur des tranches de comparateur 1 bit.

- 3. Donner les tables de vérité et le schéma en portes NAND de la tranche 1 bit de comparateur.

- 4. Comment faut-il modifier le comparateur 4 bits pour le transformer en tranche de 4 bits de comparateur ?

5. Donner le temps de retard exprimé en nombre de temps de propagation de portes NAND, noté t<sub>p</sub>, pour le comparateur 4 bits réalisé avec 4 tranches de 1 bit. Même question pour un comparateur 8 bits et pour un comparateur 16 bits.

#### 3. Additionneur BCD

En notation BCD (décimal codé binaire, chaque chiffre décimal est représenté sur un quartet ; par exemple 17 est représenté par 00010111

On veut réaliser un additionneur modulo 10 pour additionner deux chiffres BCD : pour deux chiffres BCD  $A=A_3A_2A_1A_0$  et  $B=B_3B_2B_1B_0$ , la sortie de ce circuit est  $S=S_3S_2S_1S_0$  et sa retenue de sortie est  $r_b$ , avec S=A+B modulo 10 et  $r_s=1$  si  $A+B \ge 10$ .

L'addition modulo 10 de deux nombres  $A=A_3A_2A_1A_0$  et  $B=B_3B_2B_1B_0$ peut être réalisée en deux étapes :

- Ajouter A et B (addition binaire).

- Si le résultat est supérieur ou égal à 10<sub>10</sub> ajouter 6 (il y a alors retenue pour l'étage suivant), sinon ajouter 0. Ne pas tenir compte du débordement du 2ème étage d'additionneur.

On dispose d'additionneurs binaires 4 bits dont les entrées sont  $X=X_3X_2X_1X_0$  et  $Y=Y_3Y_2Y_1Y_0$  et la retenue d'entrée  $r_e$ . Les sorties sont  $Z_3Z_2Z_1Z_0$  et la retenue de sortie  $r_s$

- 1. On injecte A et B dans l'additionneur 4 bits. Quelles sont les valeurs possibles de A+B (valeur décimale); quelles sont les valeurs de Z et  $r_s$  correspondantes ; quelles doivent être les valeurs de S et  $r_b$ ?

- 2. Donner le schéma logique de l'additionneur BCD réalisé à partir d'additionneurs binaires 4 bits et de portes NAND.

## 4. Réalisation d'un incrémenteur 4 bits (optionnel)

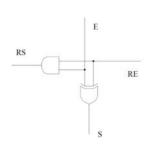

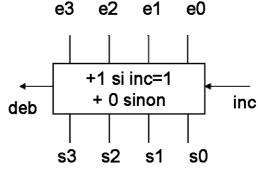

Soit le circuit Figure 3 appelé demi-additionneur, constitué d'une porte XOR et d'une porte ET. On veut réaliser un incrémenteur 4 bits (Figure 4). Les nombres X ( $e_3e_2e_1e_0$ ) et Y ( $s_3s_2s_1s_0$ ) sont des entiers non signés, compris entre 0 et 15.

Lorsque inc = 0, on a Y=X.

Lorsque inc= 1, on a Y=X+1.

Deb = 1 lorsqu'il y a débordement, c'est-à-dire inc=1 et X=15.

Figure 3: demi-additionneur

Figure 4 : Incrémenteur 4 bits

Donner un schéma simple de réalisation de l'incrémenteur 4 bits avec des demiadditionneurs

Le temps de propagation d'une porte ET est tp<sub>ET</sub> et celui d'une porte XOR est tp<sub>XOR</sub>.

• Donner le temps de retard entre les entrées et la sortie S<sub>3</sub> d'une part, entre les entrées et deb d'autre part, lorsque inc=1 en fonction de tp<sub>ET</sub> et de tp<sub>XOR</sub>..