#### GPUs et CUDA

Daniel Etiemble de@lri.fr

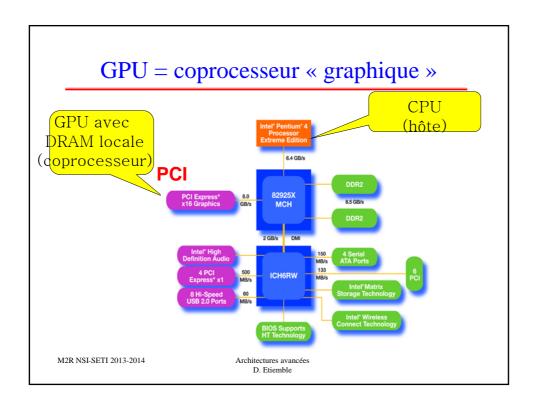

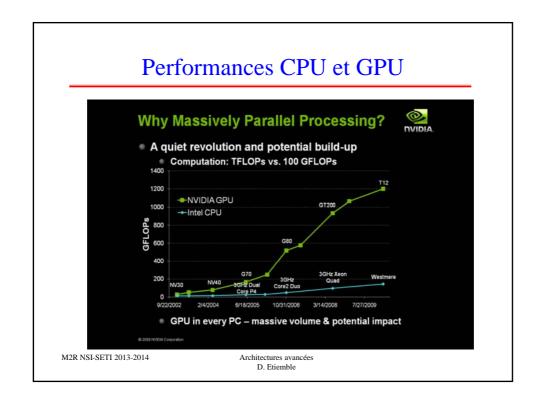

# Architecture CPU+GPU

- Architecture hétérogène

- Le CPU exécute les threads séquentiels

- Exécution séquentielle rapide

- Accès mémoire à latence faible (hiérarchie mémoire)

- Le GPU exécute le grand nombre de threads parallèles

- Exécution parallèle extensible

- Accès mémoire parallèle à très haut débit

# Les différents parallélismes

- Parallélisme d'instructions

- Exécution non ordonnée, spéculation...

- Moins d'intérêt avec les problèmes de puissance

- Parallélisme de données

- Unités vectorielles

- Importance croissante ...

SSE, AVX, Cell SPE,

Clearspeed, GPU

M2R NSI-SETI 2013-2014

Architectures avancées D. Etiemble

# Les différents parallélismes

- Parallélisme de threads

- croissant ... multithreading, multicore, manycore

- Intel Core2, AMD Phenom, Sun Niagara, STI Cell, NVIDIA Fermi, ...

Nvidia Fermi

M2R NSI-SETI 2013-

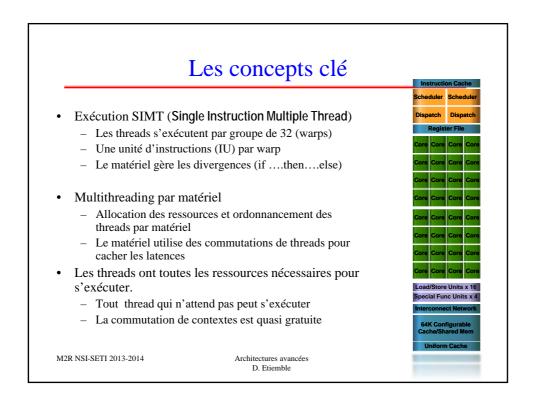

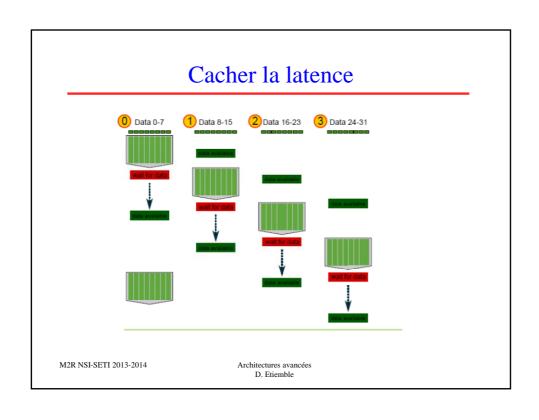

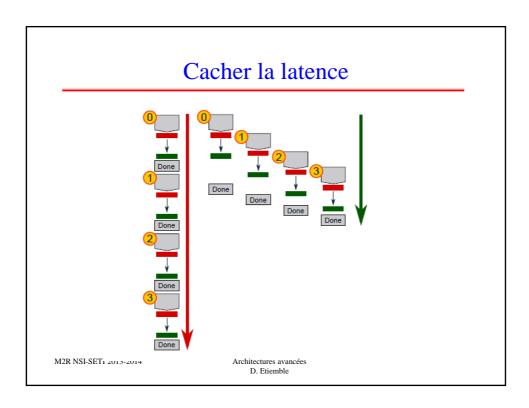

# Exécution SIMT des warps dans les SM

- Les pipelines deux accès choisissent deux warps à lancer aux cœurs parallèles

- Le warp SIMT exécute chaque instruction pour 32 threads

- Des prédicats autorisent ou non l'exécution individuelle des threads

- Une pile gère les branchements au niveau des threads

- Le calcul régulier redondant est plus rapide qu'une exécution irrégulière avec branchements

M2R NSI-SETI 2013-2014

Architectures avancées D. Etiemble

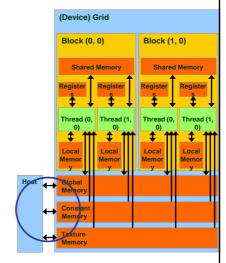

#### Modèle de programmation CUDA

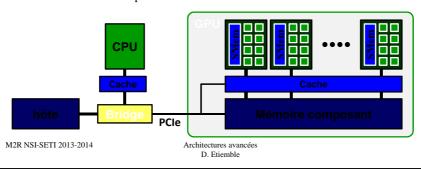

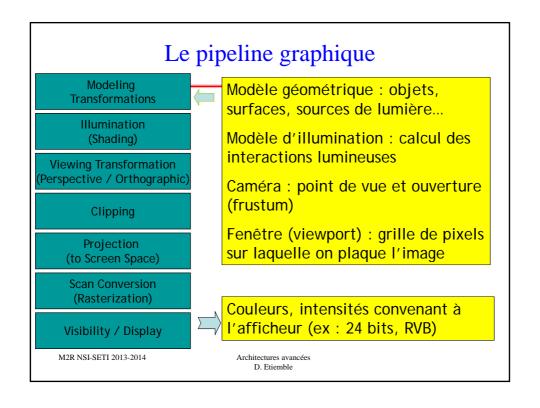

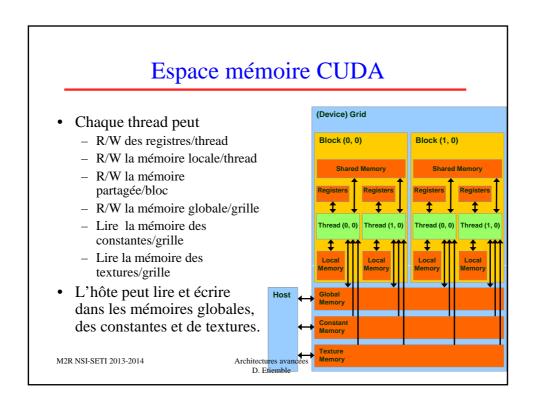

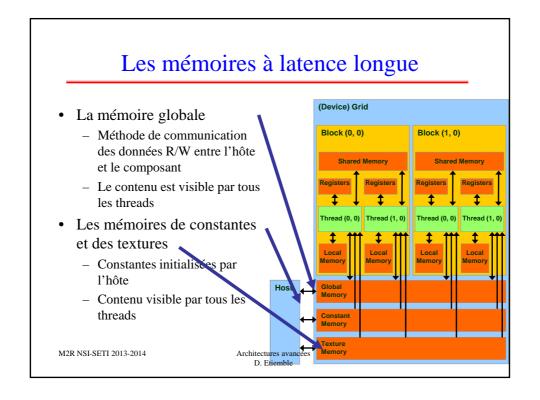

- Le GPU est vu comme un composant de calcul qui

- Est un coprocesseur du CPU ou hôte

- A sa propre DRAM (composant mémoire)

- Exécute beaucoup de threads en parallèle

- Les portions "data parallèles" d'une application sont exécutées par le composant comme des noyaux (kernels) qui s'exécutent en parallèle sur beaucoup de threads

- Les différences entre les threads GPU et CPU

- Les threads GPU sont très légers

- Très peu de surcoût de création

- Les GPU ont besoin de milliers de threads pour être efficaces.

- Les threads CPU en ont besoin de quelques uns.

M2R NSI-SETI 2013-2014

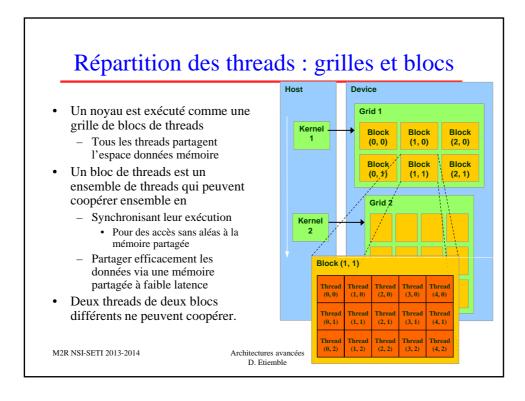

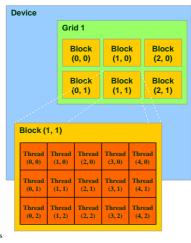

#### Identification des blocs et threads

- Les threads et les blocs ont un identifiant (ID)

- Chaque thread peut décider sur quelles données il travaille

- Blocs ID: 1D ou 2D

- Thread ID: 1D, 2D ou 3D

- Simplifie l'adressage mémoire lorsqu'on travaille sur des données multidimensionnelles

- Traitement d'images

- Résolution d'équations aux dérivées partielles sur des volumes

- ...

M2R NSI-SETI 2013-2014

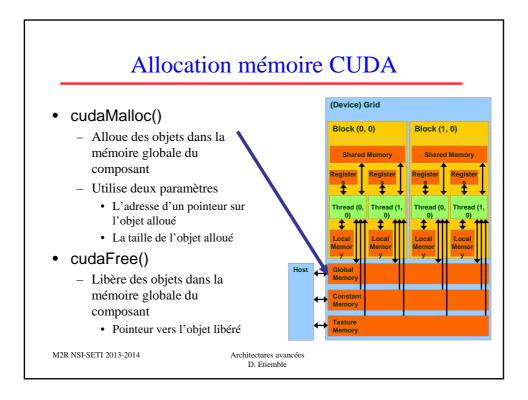

#### Allocation mémoire CUDA

- Exemple de code

- Alloue un tableau 64 x 64 de flottants simple précision

- Attache la zone mémoire alloué aux éléments Md

- "d" est souvent utilisé pour indiquer une structure de données du composant

BLOCK\_SIZE = 64; Matrix Md int size = BLOCK\_SIZE \* BLOCK\_SIZE \* sizeof(float);

cudaMalloc((void\*\*)&Md.elements, size); cudaFree(Md.elements);

M2R NSI-SETI 2013-2014

### CUDA: transfert hôte-composant

- cudaMemcpy()

- Transfert de données mémoire

- Utilise quatre paramètres

- Pointeur vers la source

- · Pointeur vers la destination

- Nombre d'octets à copier

- · Type du transferts

- Hôte vers hôte

- Hôte vers composant

- Composant vers hôte

- Composant vers composant

- Asynchrone dans CUDA 1.0

M2R NSI-SETI 2013-2014

rchitectures avancées D. Etiemble

#### CUDA: transfert hôte- composant

- Exemple de code:

- Transfère un tableau 64 \*64 de flottants simple précision

- M est dans la mémoire hôte et Md dans la mémoire du composant

- cudaMemcpyHostToDevice et cudaMemcpyDeviceToHost sont des constantes symboliques

cudaMemcpy(Md.elements, M.elements, size, cudaMemcpyHostToDevice);

cudaMemcpy(M.elements, Md.elements, size, cudaMemcpyDeviceToHost);

M2R NSI-SETI 2013-2014

#### Déclarations de fonctions CUDA

|                           | Executed on the: | Only callable from the: |

|---------------------------|------------------|-------------------------|

| device float DeviceFunc() | device           | device                  |

| global void KernelFunc()  | device           | host                    |

| host float HostFunc()     | host             | host                    |

- \_\_global\_\_ définit une fonction noyau : doit retourner void

- \_\_device\_\_ and \_\_host\_\_ peuvent être utilisés ensemble

- device\_\_ functions cannot have their address taken

- Pour les fonctions exécutées sur le composant

- Pas de récursion

- Pas de déclaration de variables statiques à l'intérieur de la fonction

- Pas de nombre variable d'arguement

M2R NSI-SETI 2013-2014

Architectures avancées D. Etiemble

# Appel d'une fonction noyau – Création de threads

• Une fonction noyau doit être appelée avec un contexte d'exécution

• Tout appel à une fonction noyau est asynchrone depuis CUDA 1.0. Une synchronisation explicite n'est pas nécessaire pour bloquer.

M2R NSI-SETI 2013-2014

#### Addition de vecteurs

• Programme C

Programme CUDA

```

_global_ void addVector (fload *a, float *b, float *c)

void addVector (fload *a, float *b,

fload *c, int N)

int i = threadIdx.x + blockDim.x*blockIdx.x;

int i, index,

c[i] = a[i] + b[i];

for (i = 0; i < N, i++) {

c[index] = a[index] + b[index];

Void main()

}

Host

// allocation & transfer data to GPU

//Excuate on N/256 blocks of 256 threads each

void main()

code

addVector << N/256, 256 >> ( d_A, d_B, d_C);

addVector(a, b, c, N);

M2R NSI-SETI 2013-2014

Architectures avancées

D. Etiemble

```

#### Addition matrices (CPU)

#### Version CPU

```

#include<iostream>

void MatrixAdd(float *A, float *B, float *C, int N) {

int index;

for(int i=0;i<N;i++) {

for(int j=0; j<N; j++) {

index = j*N + i;

C[index] = A[index] + B[index];}}

int main(int argc,char **argv){

9.

int n-1001;

float *a, *b, *c;

a = (float *)malloc(sizeof(float)*n*n);

b = (float *)malloc(sizeof(float)*n*n);

c = (float *)malloc(sizeof(float)*n*n);

10.

11.

12.

13.

for(int j=0;j<n*n;j++) {

a[j]=rand()%35;

b[j]=rand()%35;}

18.

MatrixAdd(a,b,c,n);

19.

free(a); free(b); free(c);

return 0;}

```

M2R NSI-SETI 2013-2014

### Addition de matrices (GPU)

#### Version GPU

#### M2R NSI-SETI 201

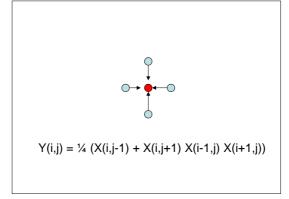

### Laplace

M2R NSI-SETI 2013-2014

# Laplace (CPU -1)

```

#include <iostream

void Laplace_h(float *A, float *B, int N) (

int index,index1,index2,index3,index4;

for(int i-1;i<N-1;i++) (

for(int j-1; j<N-1; j++) {

index = j*N + i; index1= j*N + i + 1; index2= j*N + i - 1;

index3 = (j+1)*N + i; index4 = (j-1)*N + i;

9. B[index] = 0.25*( A[index1] + A[index2] + A[index3] + A[index4]);)))

11. float Residual_h(float *A, float *B, int N){

int index;

13.

float residual, max_res-0.0;

14.

for(int i-1;i<N-1;i++) (

for(int j+1; j<N-1; j++) {

index - j*N + i;

16.

residual = A[index] - B[index];

if(residual>max_res) max_res - residual;)]

21. void Initialize(float *A, float *B, int N)(

22. // initialisation ) Architectures avancées

D. Etiemble

M2R NSI-SET

```

#### Laplace (CPU - 2)

```

23. int main(int argc,char **argv){

24.

int k-0, n-10, blocksize-64;

25.

float max_residual, *phil_h, *phi2_h;

26.

phil_h = (float *)malloc(sizeof(float)*n*n);

27.

phi2_h = (float *)malloc(sizeof(float)*n*n);

28.

Initialize(phil_h,phi2_h,n);

29.

while (k<100) [

30.

Laplace_h(phil_h,phi2_h,n);

31.

Laplace_h(phi2_h,phi1_h,n);

32.

k+-2;)

33.

max_residual - Residual_h(phil_h,phi2_h,n);

34.

printf("%d CPU residual-%f\n", k, max_residual);

35.

free(phil_h); free(phi2_h);

M2R N

Architectures avancées

D. Etiemble

```

# Laplace (GPU – 1)

```

#include "sys/time.h"

using namespace std;

__global__ void Laplace_d(float *A, float *B, int N)(

int i = blockIdx.x * blockDim.x + threadIdx.x ;

int j = blockIdx.y * blockDim.y + threadIdx.y;

int index,index1,index2,index3,index4;

index = i*N + j; index1= i*N + j + 1; index2= i*N + j - 1;

index3 = (i+1)*N + j; index4 = (i-1)*N + j;

if(i>0 && i<N-1 && j>0 && j<N-1) { B[index] = 0.25*( A[index1] +

A[index2] + A[index3] + A[index4] ); )

14. void Laplace_h(float *A, float *B, int N) (

int index, index1, index2, index3, index4;

for(int i=0;i<N;i++) {

for(int j-0; j<N; j++) {

index = i*N + j; index1= i*N + j + 1; index2= i*N + j - 1;

index3- (i+1)*N + j; index4- (i-1)*N + j;

if(i>0 && j>0 && i<N-1 && j<N-1) { B[index] = 0.25*( A[index1] +

A[index2] + A[index3] + A[index4] ); }}}

22. void Initialize(float *A, float *B, int N)

23. {/* Initialisation*/}

Architectures avancées

M2R NSI-SETI 2013-20

```

D. Etiemble

### Laplace (GPU-2)

```

int k=0, iterations=100, n=64. ThreadsPerBlock=16:

struct timeval t1_s,t1_e,t2_s,t2_e;

float *phil_h, *phi2_h; // pointers to host memory; a.k.a. CPU

float *phi1_d, *phi2_d; // pointers to device memory; a.k.a. GPU

// Allocate arrays on host and initialize

phil\_h = (float *)malloc(sizeof(float)*n*n);

phi2 h - (float *)malloc(sizeof(float)*n*n);

Initialize(phil h.phi2 h.n);

cudaMalloc((void **)&phil_d,n*n*sizeof(float));

cudaMalloc((void **)&phi2_d,n*n*sizeof(float));

dim3 dimGrid( ceil(float(n)/float(dimBlock.x)),

ceil(float(n)/float(dimBlock.y)) );

cudaMemcpy(phil_d,phil_h,n*n*sizeof(float),cudaMemcpyHostToDevice);

cudaMemcpy(phi2_d,phi2_h,n*n*sizeof(float),cudaMemcpyHostToDevice);

while (k<iterations) {

Laplace_d<<<dimGrid, dimBlock>>>(phil_d,phi2_d,n);

Laplace_d<<<dimGrid, dimBlock>>>(phi2_d,phi1_d,n);

k+-2;}

cudaMemcpy(phi2_h,phi2_d,n*n*sizeof(float),cudaMemcpyDeviceToHost);

cudaThreadSynchronize();

cudaFree (phil_d);

cudaFree (phil_d) Architectures avancées

M2R NSI-SETI 2013-20

D. Etiemble

```

#### Références

- David Kirk/NVIDIA and Wen-mei W. Hwu, 2007, ECE 498AL, University of Illinois, Urbana-Champaign

- NVIDIA., CUDA Best Practices Guide, 3.0 edition, March 2010.

- <a href="http://www.starba.se/gpgpu/workshop.pdf">http://www.starba.se/gpgpu/workshop.pdf</a>

- <a href="http://www.nvidia.com/page/technologies.html">http://www.nvidia.com/page/technologies.html</a>

M2R NSI-SETI 2013-2014