# Licence Math-Info –S4 Partiel CLM - Mars 2013

TOUS DOCUMENTS AUTORISES - CALCULETTES INTERDITES - QUATRE PARTIES INDEPENDANTES

## Partie 1 : Représentation des nombres entiers en complément à 2

- Q1) Donner l'équivalent décimal des nombres hexadécimaux en complément à deux sur 8 bits suivants :

- a. 0x7A

- b. 0xF1

- Q2) Exprimer les nombre décimaux suivants en représentation binaire en complément à deux sur 16 bits. Donner les résultats sous forme de quatre chiffres hexadécimaux.

- a. 274

- b. 1023

- c. -1

- d. -128

- Q3) Soient les additions suivantes sur des nombres 16 bits en représentation binaire en complément à 2. Donner le résultat des additions et indiquer si le résultat est correct ou s'il y a débordement.

- a. 0x1234 + 0x7654

- b. 0x8000 + 0x1234

- c. 0x9000 + 0xA000

- d. 0x2345 + 0x5678

#### Partie 2: Nombres flottants

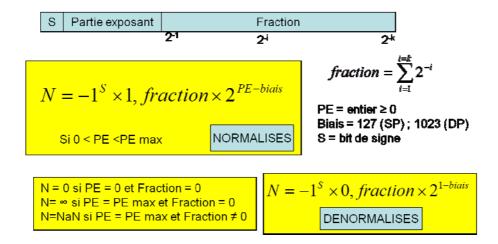

Simple précision : PE sur 8 bits, fraction sur 23 bits Double précision : PE sur 11 bits, fraction sur 52 bits.

Figure 1 : Format des nombres flottants simple précision (32 bits) et double précision (64 bits)

La figure 1 rappelle le format des nombres flottants simple précision et double précision.

- Q 4) Donner les valeurs décimales pour les flottants 32 bits suivants

- 0x43C00000

- 0xC1C00000

- Q 5) Pour transformer un flottant normalisé 32 bits en un flottant 64 bits, quelle opération faut-il effectuer

- 1. Sur la partie exposant?

- 2. Sur la fraction?

- Q6) Donner la représentation flottant double précision (sur 16 digits hexadécimaux) des nombres flottants simple précision suivants:

- 0x43C00000

- 0xC1C00000

## Partie 3 : Expressions booléennes

Q7) Donner l'expression logique simplifiée, sous forme somme de produits, pour les fonctions f0, f1, f2 et f3 de la table 1.

d correspond aux cas indifférents.

|    | <b>E3</b> | <b>E2</b> | <b>E</b> 1 | <b>E0</b> | <b>f0</b> | f1 | f2 | f3 |

|----|-----------|-----------|------------|-----------|-----------|----|----|----|

| 0  | 0         | 0         | 0          | 0         | 1         | 0  | 1  | 0  |

| 1  | 0         | 0         | 0          | 1         | 1         | 0  | d  | 1  |

| 2  | 0         | 0         | 1          | 0         | 1         | 1  | 1  | 0  |

| 3  | 0         | 0         | 1          | 1         | 1         | 1  | 1  | 0  |

| 4  | 0         | 1         | 0          | 0         | 0         | 1  | 0  | 0  |

| 5  | 0         | 1         | 0          | 1         | 0         | 1  | 0  | d  |

| 6  | 0         | 1         | 1          | 0         | 0         | 1  | 0  | 0  |

| 7  | 0         | 1         | 1          | 1         | 0         | 1  | 1  | 1  |

| 8  | 1         | 0         | 0          | 0         | 1         | 0  | 1  | d  |

| 9  | 1         | 0         | 0          | 1         | 1         | 1  | 1  | 0  |

| 10 | 1         | 0         | 1          | 0         | 0         | 1  | 0  | 1  |

| 11 | 1         | 0         | 1          | 1         | 0         | 1  | 0  | 1  |

| 12 | 1         | 1         | 0          | 0         | 0         | 0  | d  | 0  |

| 13 | 1         | 1         | 0          | 1         | 1         | 1  | 1  | 1  |

| 14 | 1         | 1         | 1          | 0         | 0         | 0  | 0  | 0  |

| 15 | 1         | 1         | 1          | 1         | 1         | 0  | 1  | d  |

Table 1

### Partie 4 : Réalisation d'un comparateur 4 bits signé.

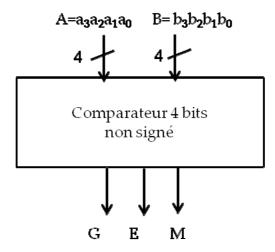

Soit un comparateur 4 bits sur des entiers non signés A et B qui donne les résultats des comparaisons G (A>B), E (A=B) et M (A<B). Plus précisément :

G = 1 si A > B et 0 sinon; E = 1 si A = B et 0 sinon; M = 1 si A < B et 0 sinon;

Figure 2 : Comparateur non signé

On veut utiliser ce comparateur pour réaliser un comparateur 4 bits sur des nombres signés en représentation en complément à 2 sur 4 bits.

- Q8) Peut on utiliser le même comparateur pour comparer d'une part, deux nombres positifs, et d'autre part, deux nombres négatifs en complément à deux ?

- Q9) Donner les valeurs de GS, ES et MS en fonction de G, E et M lorsque a3 et b3 sont de même signe. Donner les valeurs de GS, ES et MS lorsque a3 et b3 sont de signe contraire.

En déduire les expressions logiques des sorties du comparateur signé (GS, ES et MS) en fonction des bits de signe a3 et b3 et des sorties G, E et M du comparateur 4 bits non signé.