CLM-S4 D. Etiemble 2011-212

## TD 8 - Exécution des instructions

Dans ce TD, on utilise le jeu d'instruction NIOS II (processeur « logiciel » pour FPGA Altera).

# Hypothèses

Le séquencement des instructions est réalisé par une horloge.

Figure 1: signal d'horloge

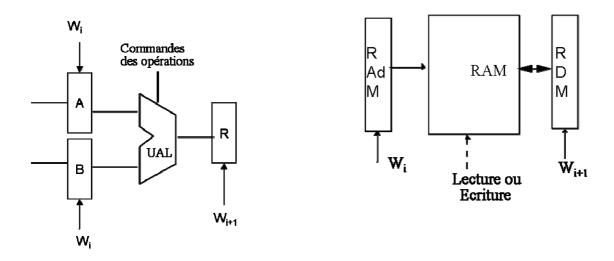

En un cycle d'horloge, on peut effectuer un transfert d'un ou plusieurs registres vers un autre registre à travers un opérateur combinatoire (UAL, comparateur) ou la mémoire. On peut bien évidemment avoir en un cycle un transfert d'un registre vers un autre registre, sans opération intermédiaire.

Figure 2: Transferts en un cycle

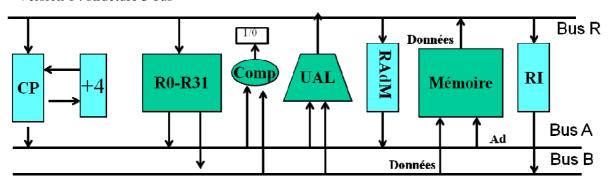

Version 1 : structure 3 bus

Figure 3 : Chemin de données (version 1).

CLM-S4 D. Etiemble 2011-212

#### Q 1) Quels sont les différentes étapes pour l'exécution des types d'instructions suivantes

- 1. Instructions arithmétiques/logiques/comparaison de format R

- 2. Instructions arithmétiques/logiques/comparaison de format I

- 3. Instructions mémoire

- 4. Instructions de branchement conditionnel

- 5. Instructions de saut (JMP Ri)

- 6. Instructions Callr (format R)

- Q 2) Donner pour chaque type d'instructions le temps d'exécution en nombre de cycles d'horloge

- Q 3) Définir l'ensemble des commandes pour contrôler l'exécution des instructions

#### Version 2

Figure 4 : chemin de données (version 2)

### Q 4) Quels sont les différentes étapes pour l'exécution des types d'instructions suivantes

- 1. Instructions arithmétiques/logiques/comparaison de format R

- 2. Instructions arithmétiques/logiques/comparaison de format I

- 3. Instructions mémoire

- 4. Instructions de branchement conditionnel

- 5. Instructions Callr

- Q 5) Donner pour chaque type d'instructions le temps d'exécution en nombre de cycles d'horloge

- Q 6) Définir l'ensemble des commandes pour contrôler l'exécution des instructions